---

# Elektronik für Informatiker

*Eine Einführung in Analoge und Digitale Systeme für Informatiker mit Elektronikgrundlagen

und Signalverarbeitung*

Prof. Dr. Stefan Bosse

Universität Koblenz - Praktische Informatik

# Analog-Digital Schnittstellen

Bisher wurden nur analoge Schaltungen betrachtet die für die z.B. für die numerische Berechnung eingesetzt werden ("Analogrechner")

# Analog-Digital Schnittstellen

Bisher wurden nur analoge Schaltungen betrachtet die für die z.B. für die numerische Berechnung eingesetzt werden ("Analogrechner")

- Isolierte Analogrechner haben häufig nur begrenzte Einsatzmöglichkeiten.

- Besser ist ein Hybridmodell aus analogen Recheneinheiten die mit digitalen (Computer) Systemen gekoppelt sind.

- Dazu benötigen wir aber Schnittstellen

- Analog-Digital Wandler

- Digital-Analog Wandler

# Analog-Digital-Wandler und Digital-Analog-Wandler

Analog-Digital-Wandler (ADC) und Digital-Analog-Wandler (DAC) sind die Schnittstellen zwischen analoger und digitaler Elektronik.

- An der Reihenfolge der Buchstaben kann man die Wandlungsrichtung erkennen:

- ein ADC bildet analoge Signale auf digitale Signale ab, während ein

- DAC digitale Signale in den analogen Bereich umsetzt.

Abb. 1. Schaltzeichen für Analog-Digital-Wandler (links) und Digital-Analog-Wandler (rechts), die Pfeile geben die Flussrichtung des Signals an

# Analog-Digital-Wandler und Digital-Analog-Wandler

## Analog

Analoge Signale sind zeitkontinuierlich und wertkontinuierlich, d.h. eine analoge Größe, z.B. eine Spannung, wird durch eine Zeitfunktion  $U(t)$  dargestellt.

## Digital

Digitale Signale sind über die Zeit gesehen durch eine Folge  $Z_1, Z_2, Z_3 \dots$  von diskreten Werten, die zu diskreten Zeiten  $t_1, t_2, t_3 \dots$  anliegen, gegeben, d.h. Spannungen werden in der Digitaltechnik durch Zahlenfolgen  $[Z_m] m \geq 1$  dargestellt.

- Am Eingang des ADC liegt die analoge Spannung  $U(t)$  an und am Ausgang wird die zugehörige Folge von Binärzahlen  $[Z_m] m \geq 1$  ausgegeben.

- Am Eingang des DAC liegt eine Folge von Binärzahlen  $[Z_m] m \geq 1$  an und es wird die zugehörige Folge von Spannungen  $[U_m] m \geq 1$  ausgegeben.

- Jeder ADC und DAC hat einen festen Eingangs- oder Ausgangsspannungsbereich  $[U_{\min}, U_{\max}]$ .

# Analog-Digital-Wandler und Digital-Analog-Wandler

Abb. 2. Wandlersymbole mit Eingangs-, Ausgangs- und Hilfsgrößen

Zur Analog-Digital- und ggfs. zur Digital-Analog-Wandlung werden zwei Hilfsgrößen benötigt, nämlich

1. ein Taktsignal  $clk$ , welches zur Realisierung diskreter Abläufe in der Zeit dient und

2. eine Referenzspannung  $U_{Ref}$ , die zur Festlegung eines Spannungsquantums  $U_{LSB}$  dient, welches beim ADC zur Abbildung der Eingangsspannung auf binäre Zahlen bzw. beim DAC zur Abbildung von Binärzahlen auf die entsprechende Spannung benutzt wird.

# Digitales Multimeter

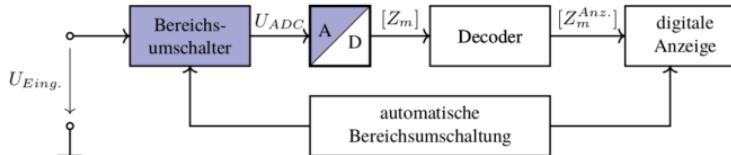

Abb. 3. Struktur eines digital anzeigenden Messgeräte

In diesem Beispiel wird eine analoge Eingangsspannung  $U_{Eing.}$  mit Hilfe eines Bereichsumschalters an den Eingangsspannungsbereich des ADC angepasst. Dem Wandler wird diese Spannung  $U_{ADC}$  eingangsseitig zugeführt und er liefert am Ausgang die entsprechenden Binärzahlen  $Z_m$ .

- Damit digitalisierte Werte  $Z_m$  angezeigt werden können, werden diese für die Anzeige in darstellbaren Code umgesetzt und an die Anzeige übergeben.

# Digitaler Funktionsgenerator

Abb. 4. Prinzip eines digitalen Funktionsgenerators (synthetische Schwingungserzeugung)

In einem ROM sind n Funktionswerte einer zu erzeugenden Funktion digital gespeichert. Beim Anlegen einer Adresse *Addr* an das ROM wird der unter der Adresse digital gespeicherte Funktionswert *Z(Addr)* auf den Eingang des DAC gelegt und schließlich als Spannungswert *U<sub>a</sub>* ( $[Z_{Addr}, clk]$ ) ausgegeben. Die Adressen des ROM werden von einem Zähler geliefert, der je nach Zählrichtung mit dem Takt *clk* vor- bzw. rückwärts zählt. Durch Erhöhen oder Verringern der Taktfrequenz kann die Frequenz der Ausgangsspannung verändert werden.

## ADDA Systeme

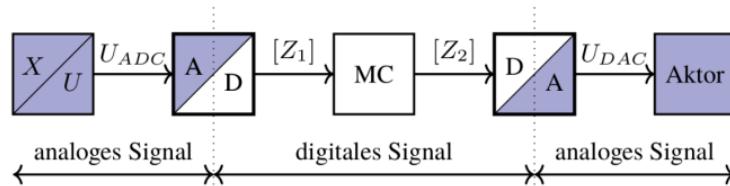

Abb. 5. Prinzip eines Analog-Digital-Analog Systems

# Wandlereigenschaften

## Lineare Wandlerkennlinie

Bei Analog-Digital-Wandlern sollen die ausgegebenen Datenworte möglichst genau das Eingangssignal, also dessen Momentanwert und Zeitverlauf, abbilden. Bei Digital-Analog-Wandlern wiederum soll die Ausgangsspannung exakt dem momentan am Eingang anliegenden Datenwort entsprechen.

## Auflösung

Kleinste auflösbare Spannung  $U_{\text{LSB}}$  ("1 Digit").

## Wandlungszeit

Die Digitalisierung der analogen Eingangsspannung benötigt eine Zeit, die Wandlungszeit  $t_W$ .

# Wandlereigenschaften

| Auflösung | Zustände  | LSB-Gewicht                  | $U_{LSB}$ für $U_{FS} = 10 \text{ V}$ |

|-----------|-----------|------------------------------|---------------------------------------|

| 4         | 16        | 0,0625                       | 625 mV                                |

| 8         | 256       | 0,039 062 5                  | 39,0625 mV                            |

| 10        | 1024      | 0,000 976 562 5              | 9,765 625 mV                          |

| 12        | 4096      | 0,000 244 140 625            | 2,441 406 25 mV                       |

| 14        | 16384     | 0,000 061 035 156 25         | 0,610 351 562 5 mV                    |

| 16        | 65536     | 0,000 015 258 789 062 5      | 152,587 890 625 $\mu\text{V}$         |

| 18        | 262144    | 0,000 003 814 697 265 625    | 38,146 972 656 25 $\mu\text{V}$       |

| 20        | 1 048 576 | 0,000 000 953 674 316 406 25 | 9,536 743 164 062 5 $\mu\text{V}$     |

Abb. 6. Auflösung, Anzahl der Zustände, LSB-Gewicht und Spannungsquantum  $U_{LSB}$

## Kennlinie eines DA Wandlers

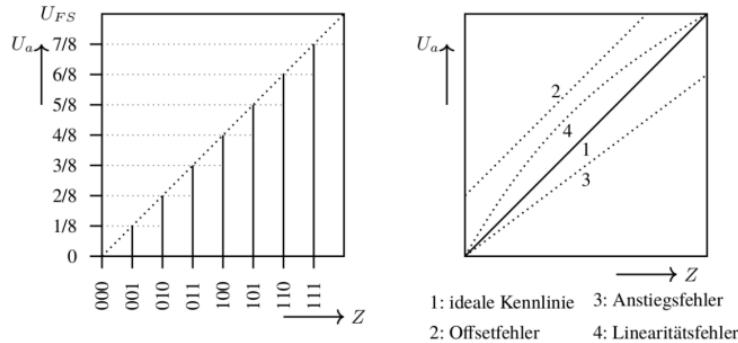

Abb. 7. Kennlinie eines 3-Bit-DAC (links) und Wandlungsfehler (rechts)

Digitale diskrete Werte führen auf analoge diskrete Werte!

## Kennlinie eines AD Wandlers

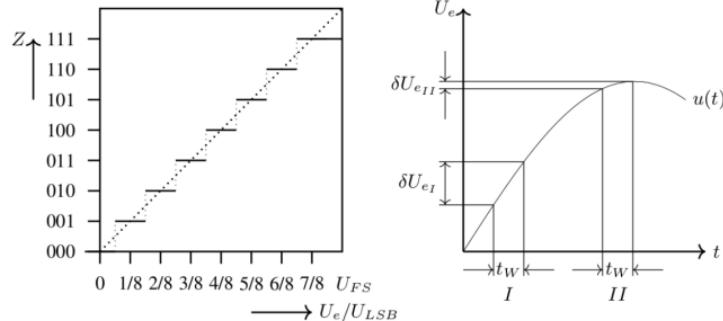

Abb. 8. Kennlinie eines 3-Bit-ADC (links) und dynamische Fehler(rechts)

Intervalle von analogen kontinuierlichen Werten führen auf diskrete Digitalwerte!

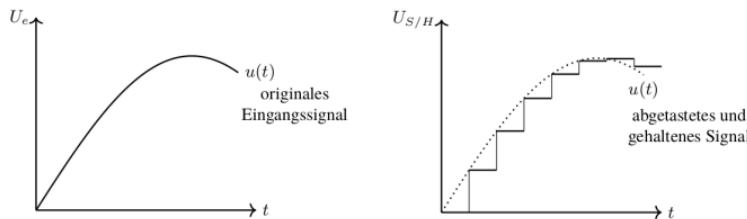

## Wandlungszeit und Signalhaltung

Die Digitalisierung der analogen Eingangsspannung benötigt eine Zeit, die Wandlungszeit  $t_W$ . Während der Wandlungszeit kann sich die Eingangsspannung je nach ihrem zeitlichen Verlauf mehr oder weniger ändern.

Damit solche Spannungsänderungen den Wandlungsprozess nicht beeinflussen, wird die Eingangsspannung abgetastet und der Abtastwert für die Zeit der Wandlung konstant gehalten. Das leisten so genannte Abtast- und Halte-Schaltungen (sample and hold circuit)

## Wandlungszeit und Signalhaltung

---

Abb. 9. (Links) Zeitlich veränderliches Signals (Rechts) Abgetastetes und gehaltenes Signal

## Periodische Abtastung und Wandlungsfrequenz

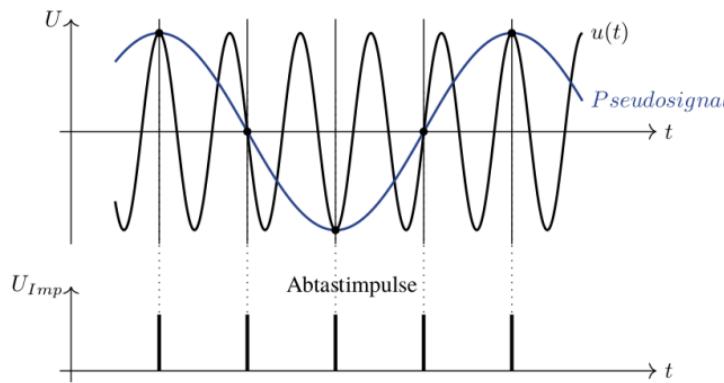

Die Wandlungszeit  $t_W$  kann bei periodischer Abtastung als Wandlungsfrequenz (Samplingfrequenz)  $f_W = 1/t_W$  verstanden werden.

Jedes zeitabhängige Signal hat ein Frequenz bzw. ein Frequenzspektrum  $f_s$ . Es muss das Nyquist Samplingtheorem eingehalten werden:  $f_s \leq 2f_W$ . Sonst...

Abb. 10. Unterabtastung und Entstehung von Scheinfrequenzen

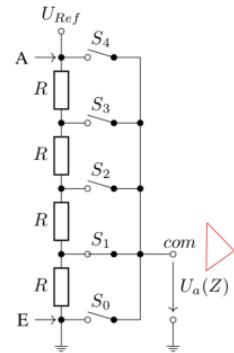

## DAC nach dem Parallelverfahren

---

Abb. 11. Parallelverfahren und Digitalpotentiometer

## DAC nach dem Parallelverfahren

Beim Parallelverfahren werden über einen Spannungsteiler alle möglichen Ausgangsspannungen mit einer Schrittweite von  $U_{\text{LSB}}$  bereitgestellt.

- Mittels eines 1-aus-n-Decoders wird der zur Binärzahl  $Z$  gehörige Schalter geschlossen, der die entsprechende Spannung abgreift und auf den Ausgang überträgt.

- Man erkennt, dass für einen  $n$ -Bit-Wandler  $2^n$  Werte und ebenso viele Schalter benötigt werden. Das Verfahren ist aufwendig und wenig gebräuchlich.

## DAC nach dem Wägeverfahren

Beim Wägeverfahren wird für jede Stelle der Binärzahl  $Z$  ein Wert bereitgestellt, wobei der kleinste Wert, das kleinste Gewicht,  $U_{\text{LSB}}$  ist.

- Die einzelnen Gewichte ergeben sich als Produkt von Potenzen von 2 und  $U_{\text{LSB}}$

- Bei einem 8-Bit-Wandler gibt es nur noch 8 Referenzen!

Abb. 12. DAC-Wägeverfahren mit gewichteten Strömen

## DAC nach dem Wägeverfahren

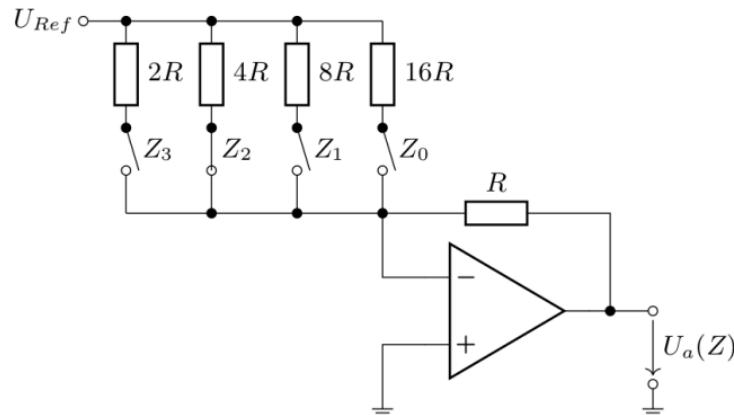

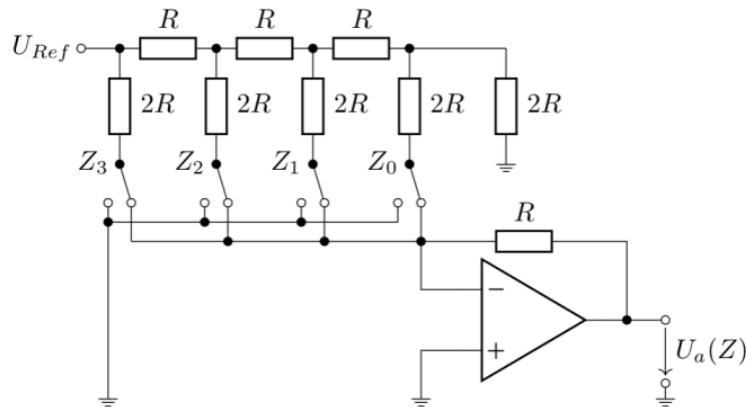

Ein anderer Weg zur Realisierung eines DAC nach dem Wägeverfahren besteht darin, die gewichteten Ströme über ein sog. R-2R-Widerstandsnetzwerk bereit zu stellen.

Abb. 13. DAC-Wägeverfahren mit R-2R-Netzwerk

## DAC nach dem Wägeverfahren

Es gilt für die Ausgangsspannung:

$$U_a(Z) = -U_{\text{Ref}} \left( \frac{Z_3}{2} + \frac{Z_2}{4} + \frac{Z_1}{8} + \frac{Z_0}{16} \right)$$

## DAC nach dem Wägeverfahren

Ein wesentlicher Unterschied der beiden Schaltungen besteht in folgendem

- In der ersten Schaltung kommen ganz unterschiedliche Widerstandswerte zum Einsatz, die alle exakt den jeweils vorgesehenen Wert haben müssen, damit der DAC fehlerfrei arbeitet. Diese Widerstandswerte genau einzuhalten, stellt ein technologisches Problem dar, insbesondere bei Wandlern mit höherer Auflösung.

- In der zweiten Schaltung mit R-2R-Netzwerk ergeben sich die Stromverhältnisse aus dem Verhältnis der Widerstände. Der Absolutwert ist nicht entscheidend. Technologisch ist die Herstellung von Widerständen mit einem bestimmten Verhältnis leichter als die Herstellung von Widerständen mit verschiedenen genauen Absolutwerten.

- Ein weiterer Vorteil des DAC mit R-2R-Netzwerk ist, dass die Referenzspannungsquelle unabhängig von der Schalterstellung immer gleich belastet wird.

# ADC nach dem Parallelverfahren

Abb. 14. DAC vice versa: Prinzip des Parallelverfahrens

Analog-Digital-Wandler, die nach dem Parallelverfahren arbeiten, sind die schnellsten und aufwendigsten Wandler. Bei ihnen wird in einem Schritt das ganze Datenwort generiert. In solchen Wandlern wird über einen genauen Spannungsteiler und analoge Komparatoren ein 000111 Digitalwort geliefert, das über einen Prioritätendekodierer in ein binäres Digitalwort umgesetzt wird.

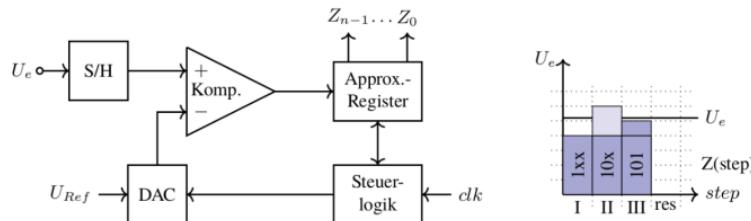

## ADC nach dem Wägeverfahren

Wandler, die nach dem Wägeverfahren arbeiten, beinhalten einen Analogkomparator, einen D/A-Wandler, ein Approximationsregister, eine Steuerlogik und einige Analogschalter. Nach dem Approximationsregister wird das Wägeverfahren auch als SAR-Verfahren bezeichnet (successive approximation register).

Abb. 15. Prinzip und Funktion eines ADC nach dem Wägeverfahren

[ad1.txt]